说到vivado的仿真确实是很有意思,不管是ISE还是Quartus都可以自己自动生成测试平台的完整构架,但是vivado不行,所有的测试代码自己写!(我反正是查了好久,都没发现vivado如何自动生成测试平台的完整构架)。

而且vivado与众不同的地方是,他的测试文件和设计文件的类型是一模一样的。不像Quartus或者ISE那样测试文件是单独的类型。

比如Quartus中测试文件都是以.vt类型的。

这也正是vivado胜人一筹的地方,他的测试文件和设计文件的类型是一模一样,这意味着vivado将不会区分测试文件和设计文件,设计的一致性得到统一。

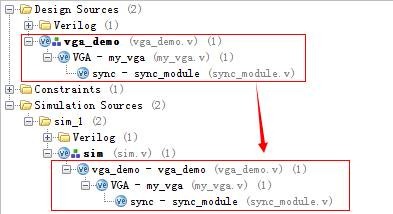

不知道读者发现没有,设计文件新建完成后,在Design Sources和Simulation Sources中都会出现我们添加的设计文件,所以vivado

的这种设计模式,道出了一个真谛——编写测试文件(及编写TestBench),和编写设计文件别无二致,都是建模!

我们要编写的测试文件,不过是基于我们的设计文件的最顶层再次建模而已。测试文件的目的就是“给些激励”、“看些反应”如此而已。

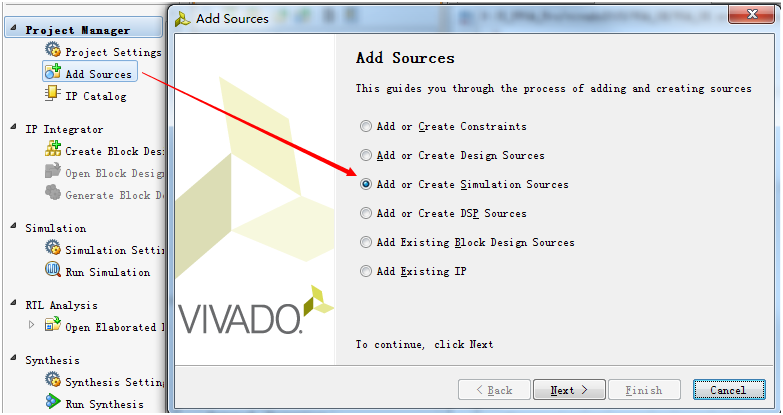

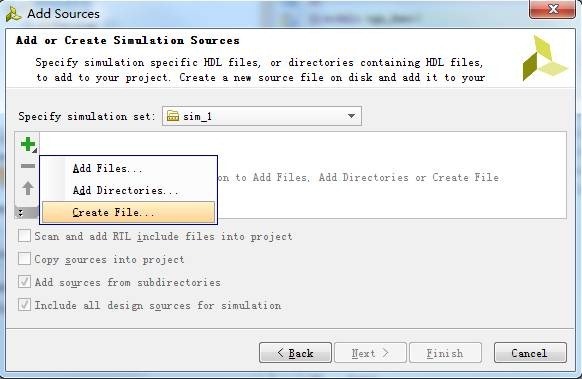

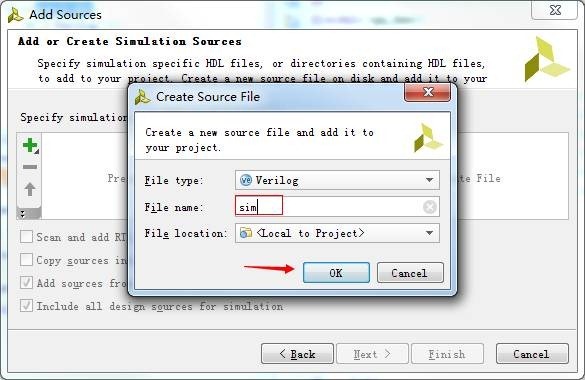

添加仿真文件:

将仿真文件设置为顶层文件:

添加代码如下:

- module sim(

- );

-

-

- reg CLK,RSTn;

- initial

- begin

- RSTn = 0; #10; RSTn = 1;

- CLK = 0; forever #5 CLK = ~CLK;

- end

-

- // 输出信号

- wire lcd_hs;

- wire lcd_vs;

- wire [3:0]lcd_red;

- wire [3:0]lcd_green;

- wire [3:0]lcd_blue;

-

- // 例化vga_demo模块

- vga_demo vga_demo(

- .CLK(CLK),

- .RSTn(RSTn),

- //硬件接口

- .lcd_hs(lcd_hs), //lcd horizontal sync

- .lcd_vs(lcd_vs), //lcd vertical sync

- //output lcd_blank, //lcd blank(L:blank)

- .lcd_red(lcd_red), //lcd red data

- .lcd_green(lcd_green), //lcd green data

- .lcd_blue(lcd_blue) //lcd blue data

- );

-

-

-

- endmodule

sim作为最顶层的文件,不需要任何输入或者输出引脚,应为他的任务只是给激励,刺激它所仿真的模块。一般情况真正需要自己写的代码其实没有多少。

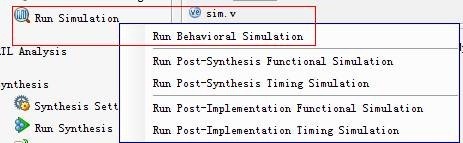

文件添加完了就可以开始仿真了:

出现如下画面:

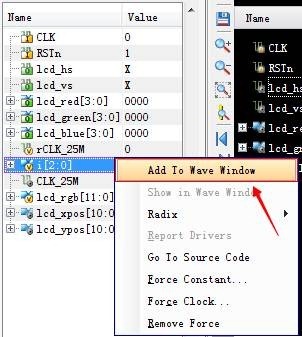

面板1显示的是工程的层次结构,当在面板1选择了一个模块后,面板2会对应变化,显示当前模块的的所以信号,这些信号都可以添加到波形显示框里观察。

一开始波形显示框里,只会显示你在顶层仿真文件中声明的信号,如果想观察其他模块内部寄存器或者引脚的值,可以通过如下方法:

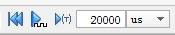

这个三个按钮,用的比较多: 这个三个按钮,用的比较多:

第一个为复位,仿真会重新开始,一般在添加了新的观察信号后使用。

第二个是run all 单击后ISIM会一直仿真知道按下暂停。根据笔者经验这个按键不要轻易按下,

一般电脑承受不起,容易卡住。所以一般会有第三个。

第三个是仿真一段时间,图中表示一次仿真20000us。相对于run all不容易卡。

|  AMD-FPGA

6101 人阅读

|

3 人回复

AMD-FPGA

6101 人阅读

|

3 人回复

AMD-FPGA

6101 人阅读

|

3 人回复

AMD-FPGA

6101 人阅读

|

3 人回复

微信客服01

微信客服01

QQ售前

QQ售前