|

1 整体概述 米联客ZYNQ系列开发平台和核心模块经过多次迭代升级,在工业自动化、水利电力控制设备、医疗图像设备等领域广泛应用,产品性能接受了广大客户的检验,稳定可靠。2021 年因芯片普遍紧缺涨价,核心模块再次升级以确保供货稳定和降低用户的使用成本。 2 硬件参数概述

| | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | 2 路(其中PS_JTAG预留未用),使用下载器进行调试和下载 | | 1 路PS 千兆以太网和 4 路 PL 千兆以太网 | | 1 路 HDMI 输出,支持DVI1.0/HDMI1.0 协议,最大输出 1080@60fps | | | | 2 路 USB 转串口,1 路PS 端和1 路 PL 端,MINI 接口 | | 1 路 TF 卡接口,一路预留的 TF1 卡接口(不焊接 EMMC 时可使用) | | | | | | | | | | | | | | 1 路 40 脚 CEP 接口,共 38 GPIO / 19 对差分 | | 2 路FEP 高速扩展接口,HR BANK,共 96 GPIO / 48 对差分 | | | | | | | | | | | | | | | | | | | | | |

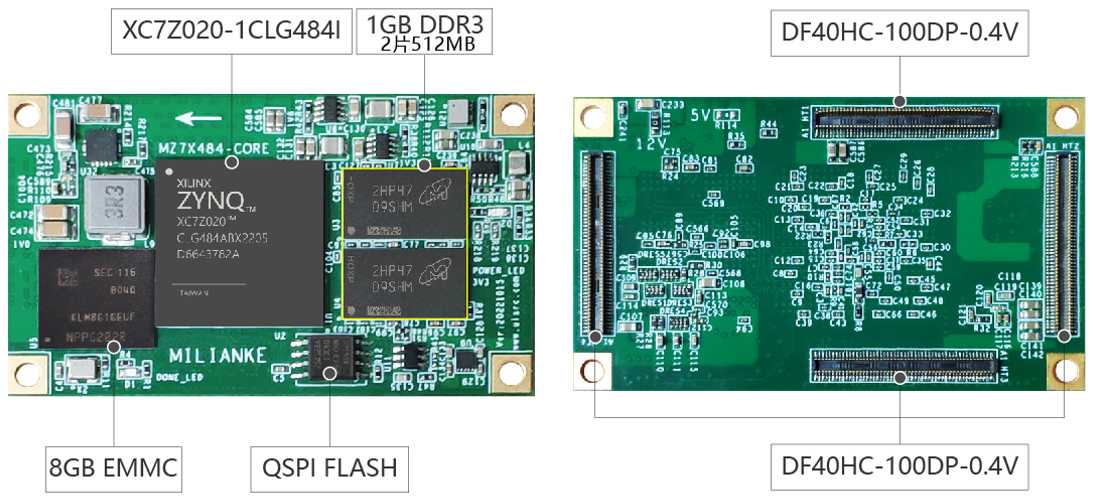

3 核心模块

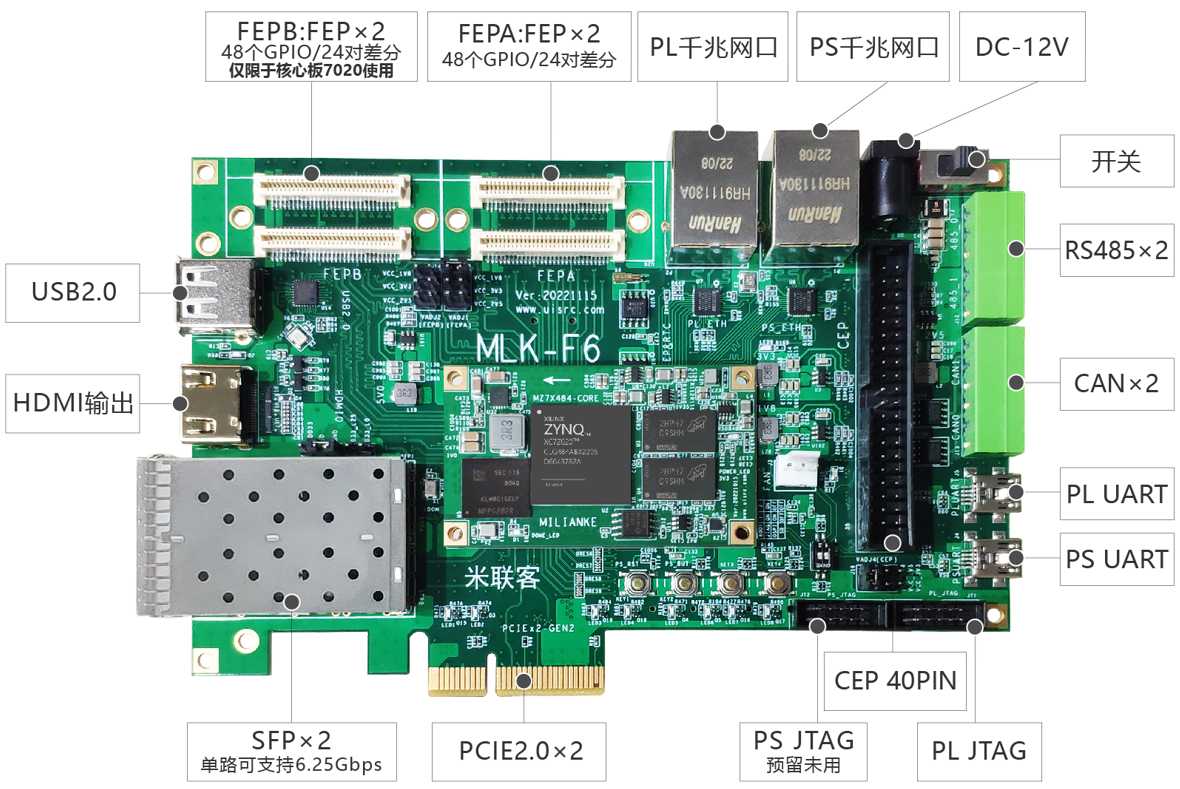

4 功能底板

5 硬件详细描述1:ZYNQ SOC

核心模块搭载了一颗 XILINX 可编程 SOC 芯片 XC7Z020CLG484-1I。该芯片集成了 ARM Cortex-A9 双核 CPU 以及可编程逻辑单元,同时具备了硬件编程和软件编程功能。

2:DDR 内存

核心模块搭载了 2 片镁光(Micron)DDR3L 内存。2 片与 ZYNQ 的 PS 内存接口相连。 单片 DDR 内存大小是 512MB ,数据接口是 16bit。PS 端 2 片内存组成 32bit 数据接口,内存大小 1GB,内存 数据主频高达 1066MHZ,数据带宽可达 1066MHz*32bit。 注意:由于 Vivado 软件中 DDR 的型号不全,为兼容核心模块使用的 DDR,使用软件时,选择 MT41K256M16 RE-125,核心模块根据市场供货,以及商业及工业级会选用以下几种型号进行量产: MT41K256M16TW-107:P(商业级 DDR 用于商业级核心模块) MT41K256M16TW-107 IT:P(工业级 DDR 用于工业级核心模块) MT41K256M16TW-107AAT:P (车规级DDR 用于工业级核心模块)

PS DDR 无需进行PIN 脚约束,使用的时候只需要对 ZYNQ IP 的DDR 配置部分正确设置相关参数。

3:QSPI4bit SPIFLASH,型号为W25Q128FV,可用于保存数据和代码。 主要技术参数:128Mbit -x1, x2,and x4 支持 -最高时钟 104 MHz, rates @ 100 MHz 4bit模式下可以达到 400Mbs -工作于 3.3V -为了正确使用 QSPI FLASH 工作于 4bit 模式, MIO[1:0,8]需要被正确设置。 MIO[8]需要通过 一个 20K 的上电阻上拉到 3.3V,让4bit FLASH 可以工作于反馈模式。 Zynq 只支持 24bit 的寻址 空间,128Mb 是通过内部 bank 的切换实现全部访问。 注意:核心板模块的 QSPI FLASH 型号根据市场货源而定,目前米联客使用以下2种型号,客户购买板卡的时候如果需要知道型号可以问下客服,一般编程可以不需要知道型号。 PS 部分的 FLASH IO 在 ZYNQ IP 中配置,通过阅读原理图,可以快速正确定位QSPI FLASH 的 MIO 的位置。

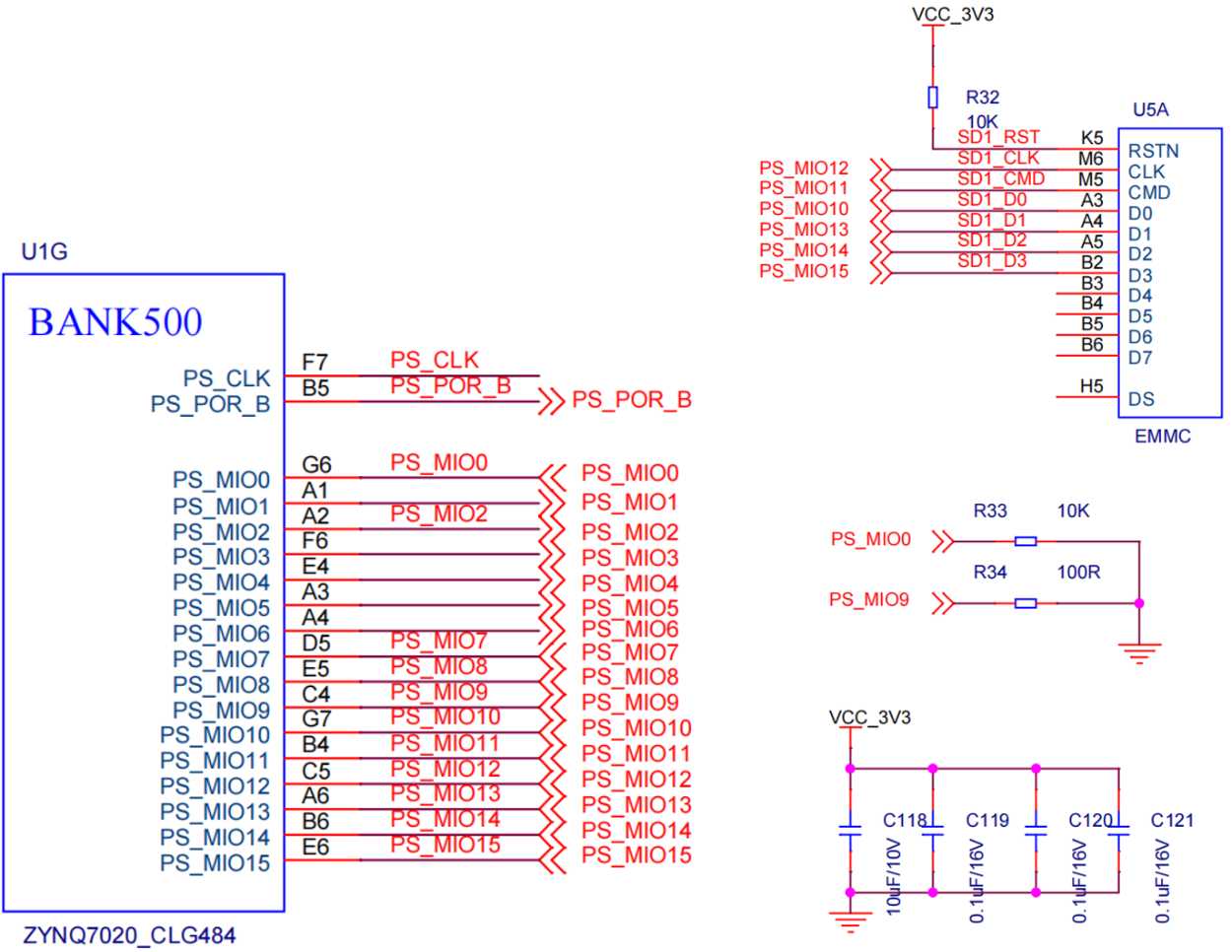

4:EMMC

核心板焊接了 8GB 大容量的 EMMC,EMMC 连接到了 ZYNQ 的 PS 端接口,接口采用SD 模式。EMMC 具备体积小,容量大,使用方便,速度快等优点,数据时钟可以达到 50MHZ。由于直接焊接在核心板上, 因此可以使用在震动或者环境相对恶劣的场合。 注意:EMMC 根据应用场合供货情况会选择不同的兼容型号目前已经量产过的EMMC 型号如下: KLM8G1GEME-B041(商业级 EMMC 用于商业级核心模块) KLM8G1GESD-B04Q(现用型号) (工业级EMMC 用于工业级级核心模块) KLMBG4GEUF-B04P(车规级 EMMC 用于工业级级核心模块) KLMBG4GEUF-B04Q(车规级EMMC 用于工业级级核心模块) PS 部分的SDIO IO在 ZYNQ IP 中配置,通过阅读原理图,可以快速正确定位 EMMC 所在的 SDIO1 的MIO的位置。

5:SD接口

开发板 TF-CARD 与主芯片 PS 部分连接,支持 SDIO 模式。TF-CARD 可以用来保存数据和程序, 如 LIUNX 操作系统。PS 部分相关的引脚是 MIO[40-47],其中包含了 TF 卡检测信号。 TF 卡由于没有写保护功能,因此写保护不起作用。由于 TF 卡工作在 3.3V ,而 MLK-L1 的 MIO[40-47]工作于 1.8V,因此使用了 TXS02612 作为电平桥接芯片。 PS 部分的 SDIO IO 在 ZYNQ IP 中配置,通过阅读原理图,可以快速正确定位 TF 卡所在的 SDIO0 的 MIO 的位置。 MLK-F6 同时将核心板 EMMC 的 IO 引出至 TF1,默认不焊接。

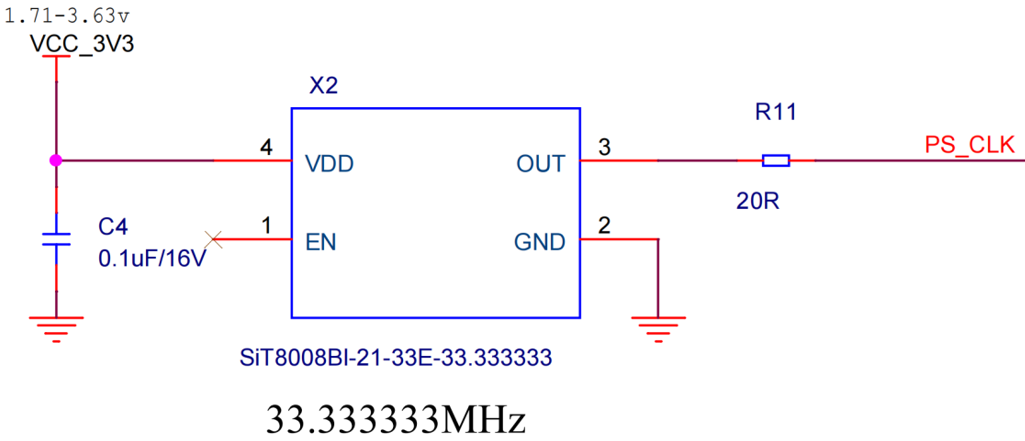

6:PS 系统时钟对于 PS 的系统输入时钟只需要在 ZYNQ IP 核中正确设置时钟频率,不需要进行 PIN 脚约束。

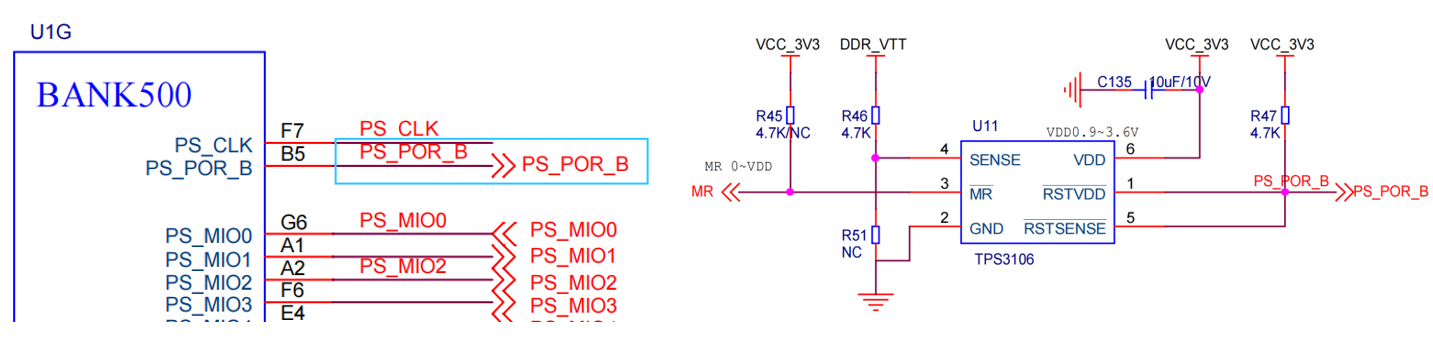

7:PL 时钟底板具备一颗 100MHZ 时钟输入到 ZYNQ 芯片 PL 端的BANK34 的 GC 管脚 P 端,供 PL 端的IO 使用。 8:上电复位开发平台上电复位信号是 PS_POR_B,此复位信号接到上电复位芯片 TPS3106K33DNVR。底板将不再把 MR 引出,用户如有需要 DDR 复位的可将 MR 单独引出。

开发平台外部复位信号是 PS_RST_B,此复位信号接到功能底板的按键输入。 9:模式开关

模式开关 SW1 在底板上,通过设置模式开关,可以实现 JTAG 模式、SD 卡模式、QSPI 模式的切换。 10:PS以太网

以太网芯片集成在功能底板上,PS 部分以太网 RGMII 接口在 ZYNQ IP 中配置,通过阅读原理图,可以快 速正确定位以RGMII 接口所在的ETH0 的MIO 的位置。 以太网的RJ-45 接口在功能底板上。 为节省成本,PS以太网和PL以太网芯片共用一个时钟芯片。

11:PL以太网

PL 集成了 1 路PL 以太网,在BANK34,该BANK 是 HR BANK,IO 电平是 3.3V 12:USB2.0接口USB2.0 使用 USB3320 芯片,连接 FPGA 的 MIO29~39&MIO46,使用排针通过跳线帽切换 ID 的上拉接 VDD33(3V3)和下拉接地(GND)达到两种模式的切换 HOST(上拉),OTG(下拉)。 13:USB_MINI串口

底板上集成了2路USB转串口,1路PS端和1路PL端。ZYNQ ARMUART 通过 CP2104 USB 转串口芯片实现和电脑通信,用于信息调试。 读者需要注意,这的 UART_TXD 实际上是数据放心是从 UART 芯片到 ZYNQ 芯片,UART_RXD 数据放心是从 ZYNQ 芯片到 UART 芯片。 14:HDMI接口

功能底板的 HDMI 输出接口直接由 FPGA 驱动,支持最大 1080@60fps 输出。 功能底板的原理图中,为了快速直观定位到FPGA 的 PIN 脚,在定义的功能网络部分有具体的 FPGA PIN 脚号。 15:EEPROM&RTC时钟DS1337 是一款低功耗,具有 56 字节非失性 RAM 的全 BCD 码时钟日历实时时钟芯片。 M24C02 是基于 I2C 总线的存储器件,遵循二线制协议,它具有接口方便,体积小,数据掉电不丢失等特点。

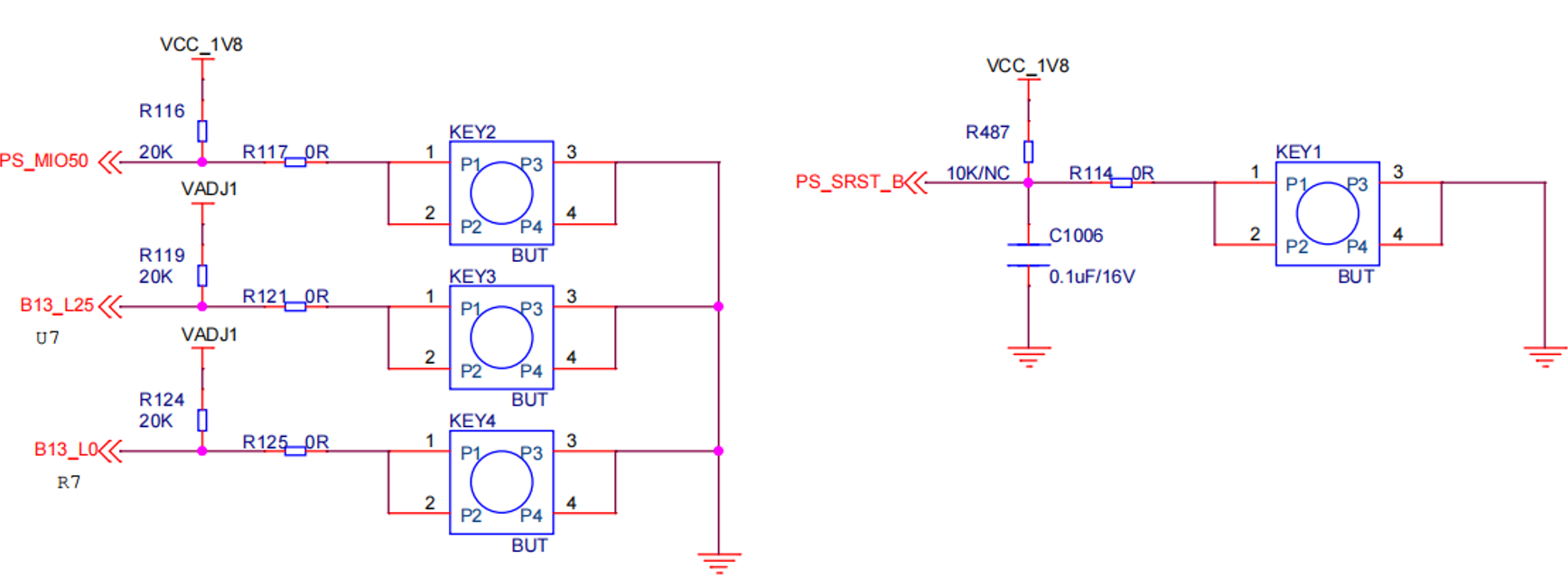

16:按键

在功能底板上有 4 个按键,1路复位按键,1路 MIO 按键,2路 PL 按键。

[url=]17:LED[/url]

在功能底板上有 8 个 LED,1 路 PS 端 LED,7 路 PL 端 LED。 18:CAN

底板上有 2 路 CAN 通信接口,连接到 PL 端 BANK34 的 IO 上,CAN 收发芯片选用了 TI 公司的SN65HVD232DR 芯片,工作在 3.3V。

19:RS485底板上有 2 路 RS485 通信接口,连接到 PL 端 BANK34 的 IO 上。 20:JTAG接口

底板集成 2 路 JTAG 接口,1 路 PS_JTAG(预留未用)和1 路 PL_JTAG,以供下载和调试。 核心板仅引出 JTAG 的 IO,未做测试接口,用户自行设计底板时需要做 JTAG 接口。 21:CEP接口

功能底板集成40PIN的CEP接口, 共 38 个 IO / 19 对差分,可用于单端 IO 的通信,也可以用于LVDS 的通信。CEP接口在BANK35上,供电来源于底板VADJ4,可以通过跳线帽选择电压(支持 1.8V, 2.5V, 3.3V)。 22:FEP高速扩展接口

底板集成 2 路 FEP 高速扩展接口,每路具有 48 个 IO / 24 对差分,其中核心板 7015 仅能使用 FEPA,核心板 7020 可以使用 FEPA和 FEPB 。

FEP 高速扩展接口可以用于单端 IO 的通信,单端 IO 最高 250M,也可以用于 LVDS 的通信。 FEPA 供电来源于底板 VADJ1 ,可以通过跳线帽选择电压(支持 1.8V, 2.5V, 3.3V) ; FEPB 供电来源于底板 VADJ2 ,可以通过跳线帽选择电压(支持 1.8V, 2.5V, 3.3V) 。 23:电源管理核心板电源 核心板集成电源管理,核心板输入电压支持5V和12V,默认12V。 核心板上电时序如下: 底板电源

MLK-F6 底板具有一个 12V 电源供电接口。此接口电源供电,可以用于实际开发和测试,请使用配套电源或稳压电源对开发板进行供电,板卡配套电源为 DC-12V/2A。为防止底板 3V3 电源先启动, 从核心板引出 PG_1V35来使能底板上的5V、3.3V、2.5V、1.8V电源。

注意: l 当用户自己设计功能底板时,确保功能底板的电源晚于核心板的电源启动,否则可能导致功能异常。 l 核心板输入电压可通过更改电阻进行调节,要注意的是配套底板只支持12V核心板供电,客户可在自己设计底板时选择5V或12V核心板输入电压。 24:结构尺寸图

核心板结构尺寸图:35(mm)x 60(mm) PCB:14 层 底板尺寸结构图:80(mm)x125(mm) PCB:8 层 25:散热片

FPGA正常工作时会产生大量的热量,开发板主芯片增加了一个散热片,防止芯片过热。若使用时还是过热可自行添加风扇,底板上有风扇的预留接口。 6 ZYNQ-XC7Z020 CLG484BANK 分布

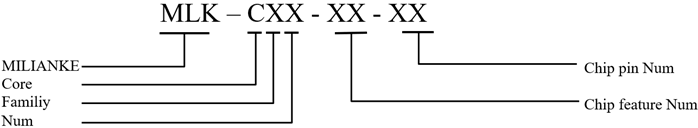

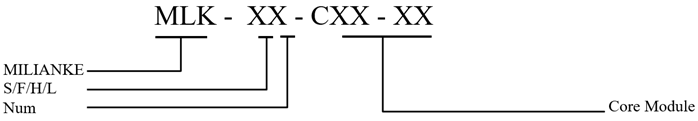

附录1:命名规则米联客硬件全新启用新的命名规则,对于老的型号,两个名字会同时使用 1 核心模块命名规则

[url=]2 开发平台命名规则S-代表单板 F-代表核心板+底板方式的FEP扩展接口的开发平台 H-代表核心板+底板方式的FMC-HPC扩展接口的开发平台 L-代表核心板+底板方式的FMC-LPC扩展接口的开发平台 [/url]

附录2:常见问题1 联系方式

技术微信:18951232035 技术电话:18951232035

官方微信公众号(新微信公众号): 2 售后1、7天无理由退货(人为原因除外) 2、质保期限:本司产品自快递签收之日起,提供一年质保服务(主芯片,比如FPGA或者CPU等除外)。 3、维修换货,需提供淘宝订单编号或合同编号,联系销售/技术支持安排退回事宜。 4、以下情形不属于质保范畴。 A:由于用户使用不当造成板子的损坏:比如电压过高造成的开发板短路,自行焊接造成的焊盘脱落、铜线起皮等 B:用户日常维护不当造成板子的损坏:比如放置不当导致线路板腐蚀、基板出现裂纹等 5、质保范畴外(上方第4条)及质保期限以外的产品,本司提供有偿维修服务。维修仅收取器件材料成本,往返运费全部由客户承担。 3 销售

销售电话:18921033576

常州溧阳总部:常州溧阳市中关村吴潭渡路雅创高科制造谷 10-1幢楼 4 在线视频5 资源下载6 软件或其他下载

|  开发平台

3582 人阅读

|

0 人回复

开发平台

3582 人阅读

|

0 人回复

开发平台

3582 人阅读

|

0 人回复

开发平台

3582 人阅读

|

0 人回复

微信客服01

微信客服01

QQ售前

QQ售前