软件版本:VIVADO2017.4 操作系统:WIN10 64bit 硬件平台:适用米联客 ZYNQ系列开发板 米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!! 2.1 概述 如同软件开发都是从“Hello Wrold!”进入编程的大门一样,这一章我们就通过HLS封装一个移位流水灯的程序熟悉HLS的开发流程,包括工程的创建,仿真,综合,封装,以及在硬件平台上的实现。通过本章,大家需要掌握HLS的基本开发流程,为下面的课程打下基础。 2.2工程创建、仿真及优化2.2.1 工程创建Step1:打开Vivado HLS开发工具,单击Creat New Project创建一个新工程,设置好工程路径和工程名,一直点击Next按照默认设置。

Step2:出现如下图所示界面,时钟周期Clock Period按照默认10ns,Uncertaintly和Solution Name均按照默认设置,点击红色圆圈部分选择芯片类型,然后点击OK。

MZ7XA-7020、MZXB开发板型号选择设置

MZ7XA -7010、MZ7XA -MINI7010开发板型号选择设置

Step3:点击Finish,出现如下界面:

Step4:右单击Source,选择New file,添加一个设计源文件。

Step5:输入文件名和选择保存的路径,然后单击保存。

Step6:双击刚才添加的文件,添加如下程序。 #include "shift_led.h" void shift_led(led_t *led_o,led_t led_i) { led_t tmp_led; cnt32_t i;//for循环的延时变量 tmp_led = led_i; for(i = 0;i < MAX_CNT;i++) { if(i==SHIFT_FLAG) { tmp_led = ((tmp_led>>3)&0x1) + ((tmp_led<<1)&0xE);//左移 *led_o = tmp_led; } } } |

Step7:按照同样的方法添加一个shift_led.h文件,添加下面的程序。 #ifndef _SHIFT_LED_H_ #define _SHIFT_LED_H_ //加入设置int自定义位宽的头文件 #include "ap_int.h" //设置灯半秒动一次,开发板时钟频率是100M //#define MAX_CNT 1000/2 //仅用于仿真,不然时间较长 #define MAX_CNT 100000000/2 #define SHIFT_FLAG MAX_CNT-2 typedef int led_t; typedef int cnt32_t;//计数器 //typedef ap_fixed<4,4> led_t; //第一个4代表总位宽,第二个4代表整数部分的位宽是4,则小数部分位宽=4-4=0 //typedef ap_fixed<32,32> cnt32_t; void shift_led(led_t *led_o,led_t led_i); #endif |

Step8:单击Test Bench,添加一个名为Test_shift_led.cpp的测试文件,并添加如下程序。 #include "shift_led.h" #include <stdio.h> using namespace std; int main() { led_t led_o; led_t led_i = 0xE;// 1110 const int SHIFT_TIME = 4; int i; for(i = 0;i < SHIFT_TIME;i++) { shift_led(&led_o,led_i); led_i = led_o; char string[25]; itoa((unsigned int)led_o&0xF,string,2);//&oxF是为了取led_o的4位,转化为二进制数出 if(i == 2) fprintf(stdout,"shift_out= 0%s\n",string);//数据对齐,高位补零 else fprintf(stdout,"shift_out= %s\n",string); } } |

2.2.2 代码综合Step1:点击Project -> Project Settings 出现下图,在Synthesis界面下选择综合的顶层函数名。

Step2:单击Browse指定工程的顶层文件,最后单击OK完成修改。

FF和LUT使用情况

Step4:我们单击方框选中的地方点击选择打开分析报告

Step5:在下图所示1的地方点击出现2所示的shift_led,点击展开后可以看到LED输入和输出位宽均为32位,我们板载是4个LED,那么该怎么去进行优化得到我们想要的结果呢?

2.2.3 代码优化点击Synthesis切换到工作空间主界面。

在shift_led.h文件中我们包含一个设置int自定义位宽的头文件"ap_int.h",我们使用ap_fixed()函数自定义int型的bit数,其函数原型为: class ap_fixed: public ap_fixed_base<_AP_W, _AP_I, true, _AP_Q, _AP_O, _AP_N>,那么这个函数怎么使用呢?它的定义如下: ap_fixed<M,N>,第一个M代表数据总位宽,N代表数据整数部分的位宽,那么小数部分的位宽即M – N;在下面的代码中,将 typedef int led_t; typedef int cnt32_t; 替换成 typedef ap_fixed<4,4> led_t; typedef ap_fixed<32,32> cnt32_t; 即可实现对端口数据位宽的约束。

另外我们再进行端口约束。约束方法如下,双击打开shift_led.cpp,在需综合的shift_led.cpp文件中的Directive目录下的led_o上右键选择Insert Directive。

因为led_o是接口,所以Directive我们选择为INTERFACE,Destination选择为Source File,那么有的会问了,这两个有什么区别吗?区别就是Source File是针对所有的Solution采用同一个优化手段,而Directive File是对当前的Solution有效,mode(optional)我们选为ap_ovld,即输出使能。

对led_i进行同样的约束,mode(optional)我们选为ap_vld。

添加后,查看shift_led.cpp,会发现多了两行代码

最终效果如下,我们再次综合,对比下进行约束以后的资源利用情况

对比发现,经过优化以后,资源利用率降低,这为以后我们对资源进行优化提供了一个参考思路。 2.2.4 仿真实现 仿真分为C代码仿真和C/RTL 联合仿真。其中C/RTL 联合仿真可以使用Vivado自带的仿真软件仿真,也可以使用第三方仿真软件Modelsim进行联合仿真。 2.2.4.1 C代码仿真

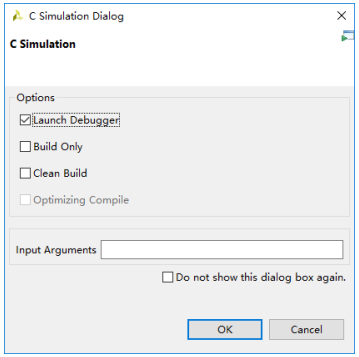

出现如下对话框,选项包括: Lauch Debugger :编译C代码,自动打开调试窗口。 Build Only:C代码编译,但是模拟器不允许。 Clean Build:在编译代码之前从项目中删除任何现有的可执行文件和目标文件。 Optimized Compile:默认情况下,设计使用调试信息进行编译,允许在调试透视图中分析编译。此选项在编译设计时使用更高级别的优化工作,但会删除调试器所需的所有信息。 这会增加编译时间,但应减少模拟运行时间。

勾选Optimized Compile,加载编译仿真窗口。

Step2:等待一段时间,仿真结果如下,我们可以看到数据循环左移了一位,达到了我们想要的实验效果。

Step3:加载调试窗口,出现调试界面,可以添加断点观察调试信号数据。

-

米联客FMC-SFP模块支持4路SFP光纤接口,最大支持10Gbps速率。可以安装到具有HPC的FMC接口开发板上使用。控

24450

-

FMC-3G SDI子卡测试1.1概述使用FMC-3GSDI子卡来实现 FPGA 通过 GTH 高速收发器从同轴电缆接收 3G-SDI 信号

26730

-

-

双十一欢乐购!米联客天猫商城和京东商城狂欢15日!2022.10.28-2022.11.11店铺推出满减优惠券!领券下单享

21110

-

1产品概述FEP-CARD-DAQ9248是一款14bits双通道65MSPS ADC采集模块,该方案采用了ADI的AD9248芯片,扩展接口

72590

-

1产品概述FEP-DAQ976X是一款14bits双通道125MSPS DAC数模转换模块,该方案采用了ADI的AD9767芯片,扩展接口

46680

-

本文在 AXI_DMA_LOOP 环路测试架构的基础上,在 DATA FIFO 端加入 FPGA 代码,对 FIFO 写,实现将 PL 端数

108613

-

在前文中我们学习了AXI总线协议,而且通过VIVADO自定义了AXI-LITE总线协议的IP CORE,并且实现了寄存器的读

69201

-

FDMA是米联客的基于AXI4总线协议定制的一个DMA控制器。有了这个IP我们可以统一实现用FPGA代码直接读写PL的D

101923

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,现在我们已经掌握了FD

123318

-

米联客FMC-SFP模块支持4路SFP光纤接口,最大支持10Gbps速率。可以安装到具有HPC的FMC接口开发板上使用。控

24450

-

FMC-3G SDI子卡测试1.1概述使用FMC-3GSDI子卡来实现 FPGA 通过 GTH 高速收发器从同轴电缆接收 3G-SDI 信号

26730

-

-

双十一欢乐购!米联客天猫商城和京东商城狂欢15日!2022.10.28-2022.11.11店铺推出满减优惠券!领券下单享

21110

-

1产品概述FEP-CARD-DAQ9248是一款14bits双通道65MSPS ADC采集模块,该方案采用了ADI的AD9248芯片,扩展接口

72590

-

1产品概述FEP-DAQ976X是一款14bits双通道125MSPS DAC数模转换模块,该方案采用了ADI的AD9767芯片,扩展接口

46680

-

本文在 AXI_DMA_LOOP 环路测试架构的基础上,在 DATA FIFO 端加入 FPGA 代码,对 FIFO 写,实现将 PL 端数

108613

-

在前文中我们学习了AXI总线协议,而且通过VIVADO自定义了AXI-LITE总线协议的IP CORE,并且实现了寄存器的读

69201

-

FDMA是米联客的基于AXI4总线协议定制的一个DMA控制器。有了这个IP我们可以统一实现用FPGA代码直接读写PL的D

101923

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,现在我们已经掌握了FD

123318

-

米联客FMC-SFP模块支持4路SFP光纤接口,最大支持10Gbps速率。可以安装到具有HPC的FMC接口开发板上使用。控

24450

-

FMC-3G SDI子卡测试1.1概述使用FMC-3GSDI子卡来实现 FPGA 通过 GTH 高速收发器从同轴电缆接收 3G-SDI 信号

26730

-

-

双十一欢乐购!米联客天猫商城和京东商城狂欢15日!2022.10.28-2022.11.11店铺推出满减优惠券!领券下单享

21110

-

1产品概述FEP-CARD-DAQ9248是一款14bits双通道65MSPS ADC采集模块,该方案采用了ADI的AD9248芯片,扩展接口

72590

-

1产品概述FEP-DAQ976X是一款14bits双通道125MSPS DAC数模转换模块,该方案采用了ADI的AD9767芯片,扩展接口

46680

-

本文在 AXI_DMA_LOOP 环路测试架构的基础上,在 DATA FIFO 端加入 FPGA 代码,对 FIFO 写,实现将 PL 端数

108613

-

在前文中我们学习了AXI总线协议,而且通过VIVADO自定义了AXI-LITE总线协议的IP CORE,并且实现了寄存器的读

69201

-

FDMA是米联客的基于AXI4总线协议定制的一个DMA控制器。有了这个IP我们可以统一实现用FPGA代码直接读写PL的D

101923

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,现在我们已经掌握了FD

123318

-

1.1 FPGA技术背景笔者也是在偶然的机缘下接触到FPGA的,当初只有感性的认识就是FPGA速

1124320

-

淘宝购买链接:https://item.taobao.com/item.htm?spm=a1z10.5-c-s.w4002-18659455309

1534215

-

在前面的课程种,我们已经提供了FDMA和XDMA配合使用,应用于PCIE传图的方案。但是前面

14814115

-

8B/10B编码是1983年由IBM公司的Al Widmer和PeterFranaszek所提出的数据传输编码标准,

821210

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,

123308

-

软件版本:VIVADO2017.4操作系统:WIN10 64bit硬件平台:适用米联客 ZYNQ系列开发板米

252068

-

淘宝购买连接:https://item.taobao.com/item.htm?spm=a1z10.5-c-s.w4002-18659455309

101808

-

1概述在米联客老版本的MIA701开发板(2017版本)中,米联开源了1套原创的UDP IP协议栈。

136608

-

1、电源改动版本使用电压输入电压范围201712275V4.7-5.2V201909185V2.0-16V新版本采用

69278

-

前面我们完成了一个PCIE中断采集图像的方案,但是很多应用中我们需要采集分析ADC的数

111188

-

1.1 FPGA技术背景笔者也是在偶然的机缘下接触到FPGA的,当初只有感性的认识就是FPGA速

1124320

-

淘宝购买链接:https://item.taobao.com/item.htm?spm=a1z10.5-c-s.w4002-18659455309

1534215

-

在前面的课程种,我们已经提供了FDMA和XDMA配合使用,应用于PCIE传图的方案。但是前面

14814315

-

8B/10B编码是1983年由IBM公司的Al Widmer和PeterFranaszek所提出的数据传输编码标准,

821310

-

1概述在米联客老版本的MIA701开发板(2017版本)中,米联开源了1套原创的UDP IP协议栈。

136618

-

1、电源改动版本使用电压输入电压范围201712275V4.7-5.2V201909185V2.0-16V新版本采用

69288

-

前面我们完成了一个PCIE中断采集图像的方案,但是很多应用中我们需要采集分析ADC的数

111188

-

本章讲解使用PL端以太网口实现UDP通信。开发板中实现千兆网 UDP 传输的基本逻辑框架如

153488

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,

123328

-

软件版本:VIVADO2017.4操作系统:WIN10 64bit硬件平台:适用米联客 ZYNQ系列开发板米

252088

-

1.1 FPGA技术背景笔者也是在偶然的机缘下接触到FPGA的,当初只有感性的认识就是FPGA速

1124320

-

淘宝购买链接:https://item.taobao.com/item.htm?spm=a1z10.5-c-s.w4002-18659455309

1534215

-

在前面的课程种,我们已经提供了FDMA和XDMA配合使用,应用于PCIE传图的方案。但是前面

14814415

-

8B/10B编码是1983年由IBM公司的Al Widmer和PeterFranaszek所提出的数据传输编码标准,

821310

-

1概述在米联客老版本的MIA701开发板(2017版本)中,米联开源了1套原创的UDP IP协议栈。

136618

-

1、电源改动版本使用电压输入电压范围201712275V4.7-5.2V201909185V2.0-16V新版本采用

69298

-

前面我们完成了一个PCIE中断采集图像的方案,但是很多应用中我们需要采集分析ADC的数

111188

-

本章讲解使用PL端以太网口实现UDP通信。开发板中实现千兆网 UDP 传输的基本逻辑框架如

153498

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,

123328

-

软件版本:VIVADO2017.4操作系统:WIN10 64bit硬件平台:适用米联客 ZYNQ系列开发板米

252108

-

米联客FMC-SFP模块支持4路SFP光纤接口,最大支持10Gbps速率。可以安装到具有HPC的FMC

24450

-

FMC-3G SDI子卡测试1.1概述使用FMC-3GSDI子卡来实现 FPGA 通过 GTH 高速收发器从同轴

26730

-

双十一欢乐购!米联客天猫商城和京东商城狂欢15日!2022.10.28-2022.11.11店铺推出满

21110

-

1产品概述FEP-CARD-DAQ9248是一款14bits双通道65MSPS ADC采集模块,该方案采用了ADI的

72590

-

1产品概述FEP-DAQ976X是一款14bits双通道125MSPS DAC数模转换模块,该方案采用了ADI的

46680

-

本文在 AXI_DMA_LOOP 环路测试架构的基础上,在 DATA FIFO 端加入 FPGA 代码,对 FIFO

108613

-

在前文中我们学习了AXI总线协议,而且通过VIVADO自定义了AXI-LITE总线协议的IP CORE,

69201

-

FDMA是米联客的基于AXI4总线协议定制的一个DMA控制器。有了这个IP我们可以统一实现用F

101923

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,

123318

-

基于FDMA可以完成很多数据读写存储类的应用,本文将展示通过FDMA读写AXI-BRAM

本文实

63341

-

米联客FMC-SFP模块支持4路SFP光纤接口,最大支持10Gbps速率。可以安装到具有HPC的FMC

24450

-

FMC-3G SDI子卡测试1.1概述使用FMC-3GSDI子卡来实现 FPGA 通过 GTH 高速收发器从同轴

26740

-

双十一欢乐购!米联客天猫商城和京东商城狂欢15日!2022.10.28-2022.11.11店铺推出满

21130

-

1产品概述FEP-CARD-DAQ9248是一款14bits双通道65MSPS ADC采集模块,该方案采用了ADI的

72600

-

1产品概述FEP-DAQ976X是一款14bits双通道125MSPS DAC数模转换模块,该方案采用了ADI的

46690

-

本文在 AXI_DMA_LOOP 环路测试架构的基础上,在 DATA FIFO 端加入 FPGA 代码,对 FIFO

108623

-

在前文中我们学习了AXI总线协议,而且通过VIVADO自定义了AXI-LITE总线协议的IP CORE,

69221

-

FDMA是米联客的基于AXI4总线协议定制的一个DMA控制器。有了这个IP我们可以统一实现用F

101943

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,

123338

-

基于FDMA可以完成很多数据读写存储类的应用,本文将展示通过FDMA读写AXI-BRAM

本文实

63351

-

米联客FMC-SFP模块支持4路SFP光纤接口,最大支持10Gbps速率。可以安装到具有HPC的FMC

24460

-

FMC-3G SDI子卡测试1.1概述使用FMC-3GSDI子卡来实现 FPGA 通过 GTH 高速收发器从同轴

26750

-

双十一欢乐购!米联客天猫商城和京东商城狂欢15日!2022.10.28-2022.11.11店铺推出满

21130

-

1产品概述FEP-CARD-DAQ9248是一款14bits双通道65MSPS ADC采集模块,该方案采用了ADI的

72600

-

1产品概述FEP-DAQ976X是一款14bits双通道125MSPS DAC数模转换模块,该方案采用了ADI的

46690

-

本文在 AXI_DMA_LOOP 环路测试架构的基础上,在 DATA FIFO 端加入 FPGA 代码,对 FIFO

108623

-

在前文中我们学习了AXI总线协议,而且通过VIVADO自定义了AXI-LITE总线协议的IP CORE,

69231

-

FDMA是米联客的基于AXI4总线协议定制的一个DMA控制器。有了这个IP我们可以统一实现用F

101943

-

在前文的实验中我们详细介绍了FDMA的使用方法,以及使用了AXI-BRAM演示了FDMA的使用,

123338

-

基于FDMA可以完成很多数据读写存储类的应用,本文将展示通过FDMA读写AXI-BRAM

本文实

63361

-

优质服务商家

严格准入,海量云服务

-

7*8小时在线服务

实时咨询,安心购物

-

专业测试 品质保证

安全监测,保证品质

-

退款售后无忧

不满意可退款

-

|